# **COMW5** Datasheet

Version 1.0.5

© Copyright 2013 W IZnet Co., Ltd. All rights reserved.

# COMW5

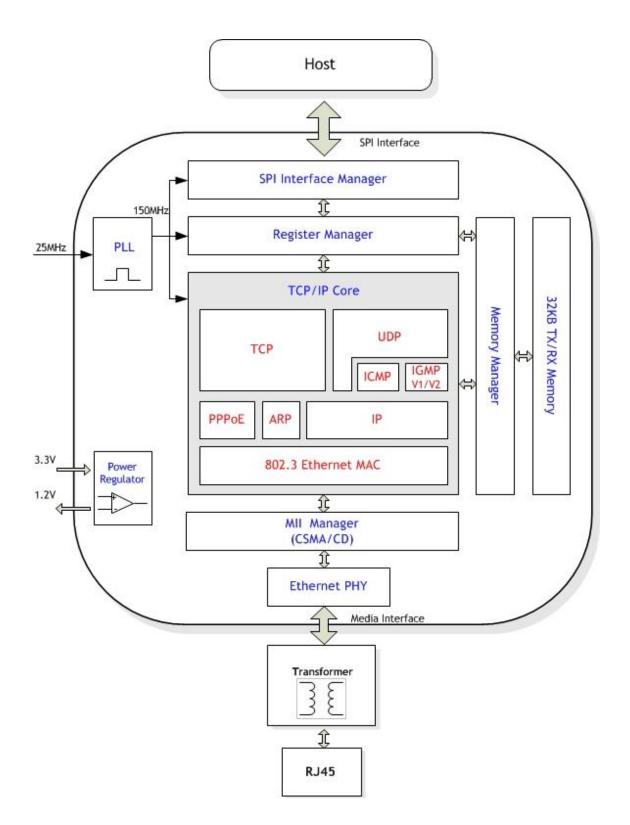

The COMW5 chip is a Hardwired TCP/IP embedded Ethernet controller that provides easier Internet connection to embedded systems. COMW5 enables users to have the Internet connectivity in their applications just by using the single chip in which TCP/IP stack, 10/100 Ethernet MAC and PHY embedded.

WIZnet's Hardwired TCP/IP is the market-proven technology that supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE protocols. COMW5 embeds the 32Kbyte internal memory buffer for the Ethernet packet processing. If you use COMW5, you can implement the Ethernet application just by adding the simple socket program. It's faster and easier way rather than using any other Embedded Ethernet solution. Users can use 8 independent hardware sockets simultaneously.

SPI (Serial Peripheral Interface) is provided for easy integration with the external MCU. The COMW5's SPI supports 80 MHz speed and new efficient SPI protocol for the high speed network communication. In order to reduce power consumption of the system, COMW5 provides WOL (Wake on LAN) and power down mode.

# Features

- Supports Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Supports Power down mode

- Supports Wake on LAN over UDP

- Supports High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for TX/RX Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Supports Auto Negotiation (Full and half duplex, 10 and 100-based )

- Not supports IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- LED outputs (Full/Half duplex, Link, Speed, Active)

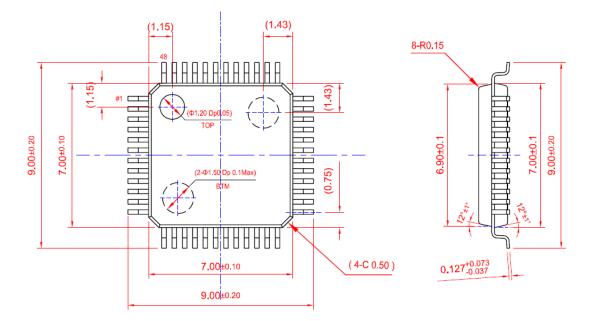

- 48 Pin LQFP Lead-Free Package (7x7mm, 0.5mm pitch)

# **Target Applications**

COMW5 is suitable for the following embedded applications:

- Home Network Devices: Set-Top Boxes, PVRs, Digital Media Adapters

- Serial-to-Ethernet: Access Controls, LED displays, Wireless AP relays, etc.

- Parallel-to-Ethernet: POS / Mini Printers, Copiers

- USB-to-Ethernet: Storage Devices, Network Printers

- GPIO-to-Ethernet: Home Network Sensors

- Security Systems: DVRs, Network Cameras, Kiosks

- Factory and Building Automations

- Medical Monitoring Equipment

- Embedded Servers

# **Block Diagram**

# Table of Contents

| 1 | 1 Pin Assignment |                      |                                                |  |  |  |  |  |  |  |  |

|---|------------------|----------------------|------------------------------------------------|--|--|--|--|--|--|--|--|

|   | 1.1              | Pin Descriptions8    |                                                |  |  |  |  |  |  |  |  |

| 2 | HOS              | IOST Interface       |                                                |  |  |  |  |  |  |  |  |

|   | 2.1              | SPI Operation Mode 1 |                                                |  |  |  |  |  |  |  |  |

|   | 2.2              | SPI I                | Frame                                          |  |  |  |  |  |  |  |  |

|   |                  | 2.2.1                | Address Phase 15                               |  |  |  |  |  |  |  |  |

|   |                  | 2.2.2                | Control Phase                                  |  |  |  |  |  |  |  |  |

|   |                  | 2.2.3                | Data Phase                                     |  |  |  |  |  |  |  |  |

|   | 2.3              | Vari                 | able Length Data Mode (VDM)                    |  |  |  |  |  |  |  |  |

|   |                  | 2.3.1                | Write Access in VDM                            |  |  |  |  |  |  |  |  |

|   |                  | 2.3.2                | Read Access in VDM                             |  |  |  |  |  |  |  |  |

|   | 2.4              | Fixe                 | d Length Data Mode (FDM)25                     |  |  |  |  |  |  |  |  |

|   |                  | 2.4.1                | Write Access in FDM                            |  |  |  |  |  |  |  |  |

|   |                  | 2.4.2                | Read Access in FDM                             |  |  |  |  |  |  |  |  |

| 3 | Reg              | ister and            | Memory Organization28                          |  |  |  |  |  |  |  |  |

|   | 3.1              | Com                  | nmon Register Block                            |  |  |  |  |  |  |  |  |

|   | 3.2              | Sock                 | et Register Block                              |  |  |  |  |  |  |  |  |

|   | 3.3              | Men                  | nory                                           |  |  |  |  |  |  |  |  |

| 4 | Reg              | ister Desc           | riptions                                       |  |  |  |  |  |  |  |  |

|   | 4.1              | Com                  | 1 mon Registers                                |  |  |  |  |  |  |  |  |

|   | 4.2              | Sock                 | et Registers                                   |  |  |  |  |  |  |  |  |

| 5 | Elec             | trical Spe           | ecifications                                   |  |  |  |  |  |  |  |  |

|   | 5.1              | Abso                 | olute Maximum Ratings 61                       |  |  |  |  |  |  |  |  |

|   | 5.2              | Abso                 | olute Maximum Ratings (Electrical Sensitivity) |  |  |  |  |  |  |  |  |

|   | 5.3              | DC (                 | Characteristics                                |  |  |  |  |  |  |  |  |

|   | 5.4              | Pow                  | er Dissipation                                 |  |  |  |  |  |  |  |  |

|   | 5.5              | AC (                 | Characteristics                                |  |  |  |  |  |  |  |  |

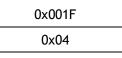

|   |                  | 5.5.1                | Reset Timing                                   |  |  |  |  |  |  |  |  |

|   |                  | 5.5.2 Wake up Time   |                                                |  |  |  |  |  |  |  |  |

|   |                  | 5.5.3                | Crystal Characteristics                        |  |  |  |  |  |  |  |  |

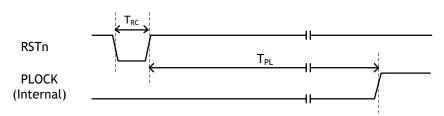

|   |                  | 5.5.4                | SPI Timing                                     |  |  |  |  |  |  |  |  |

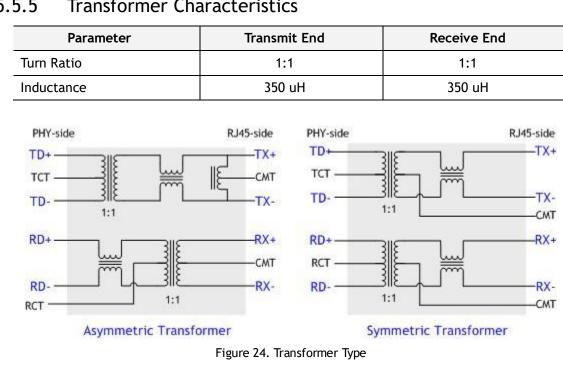

|   |                  | 5.5.5                | Transformer Characteristics                    |  |  |  |  |  |  |  |  |

|   |                  | 5.5.6                | MDIX                                           |  |  |  |  |  |  |  |  |

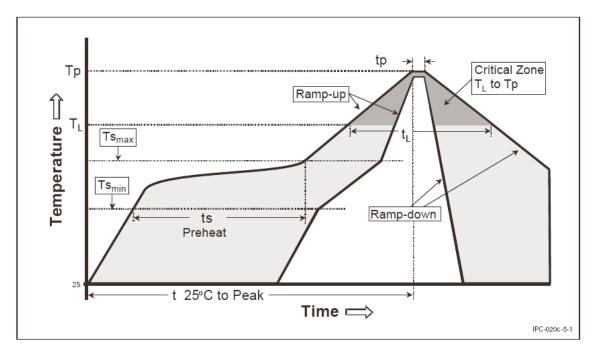

| 6 | IR R             | eflow Ten            | nperature Profile (Lead-Free)66                |  |  |  |  |  |  |  |  |

| 7 | Pacl             | kage Desc            | riptions                                       |  |  |  |  |  |  |  |  |

| C | )ocur            | ment Hist            | ory Information                                |  |  |  |  |  |  |  |  |

# Table of Figures

| Figure 1. COMW5 Pin Layout                                                             |

|----------------------------------------------------------------------------------------|

| Figure 2. External reference resistor 12                                               |

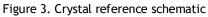

| Figure 3. Crystal reference schematic 12                                               |

| Figure 4. Variable Length Data Mode (SCSn controlled by the host) 13                   |

| Figure 5. Fixed Length Data Mode (SCSn is always connected by Ground) 13               |

| Figure 6. SPI Mode 0 & 3 14                                                            |

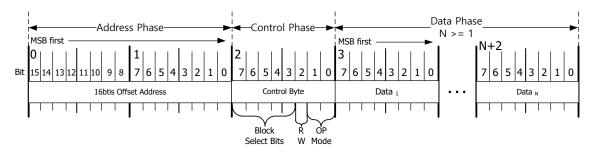

| Figure 7. SPI Frame Format 15                                                          |

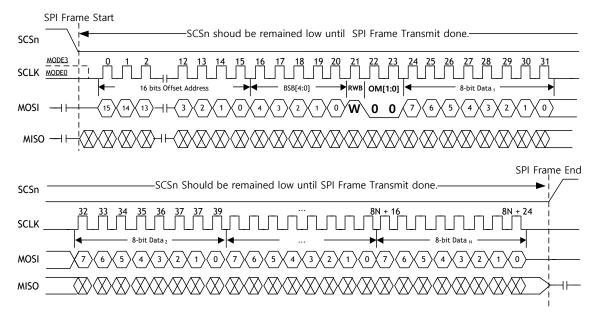

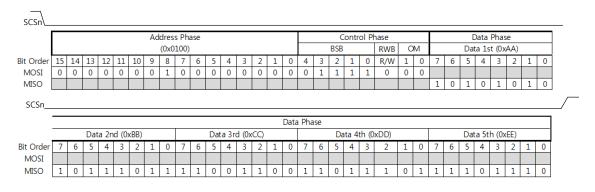

| Figure 8. Write SPI Frame in VDM mode 19                                               |

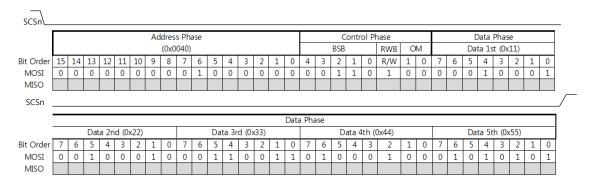

| Figure 9. SIMR Register Write in VDM Mode                                              |

| Figure 10. 5 Byte Data Write at 1th Socket's TX Buffer Block $0x0040$ in VDM mode . 21 |

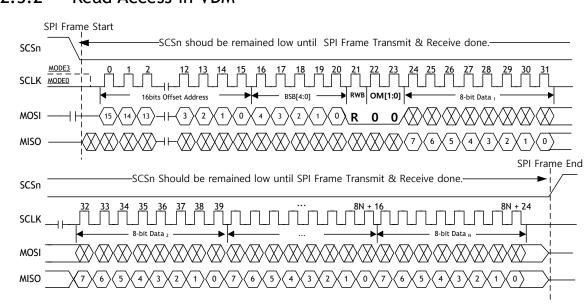

| Figure 11. Read SPI Frame in VDM mode 22                                               |

| Figure 12. S7_SR Read in VDM Mode23                                                    |

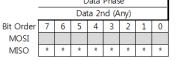

| Figure 13. 5 Byte Data Read at Socket 3 RX Buffer Block 0x0100 in VDM mode 24          |

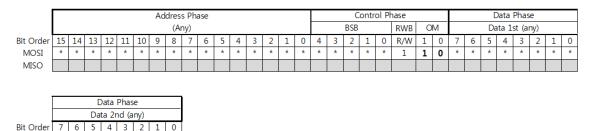

| Figure 14. 1 Byte Data Write SPI Frame in FDM mode                                     |

| Figure 15. 2 Bytes Data Write SPI Frame in FDM mode                                    |

| Figure 16. 4 Bytes Data Write SPI Frame in FDM mode                                    |

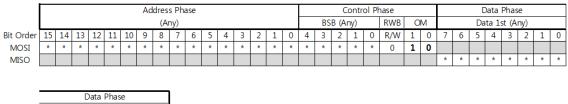

| Figure 17. 1 Byte Data Read SPI Frame in FDM mode                                      |

| Figure 18. 2 Bytes Data Read SPI Frame in FDM mode                                     |

| Figure 19. 4 Bytes Data Read SPI Frame in FDM mode 27                                  |

| Figure 20. Register & Memory Organization                                              |

| Figure 21. INTLEVEL Timing                                                             |

| Figure 22. Reset Timing                                                                |

| Figure 23. SPI Timing 64                                                               |

| Figure 24. Transformer Type                                                            |

| Figure 25. IR Reflow Temperature                                                       |

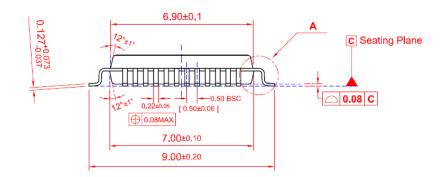

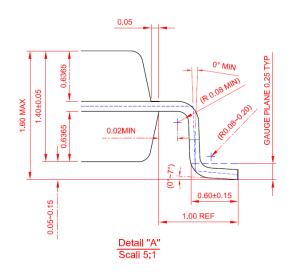

| Figure 26. Package Dimensions                                                          |

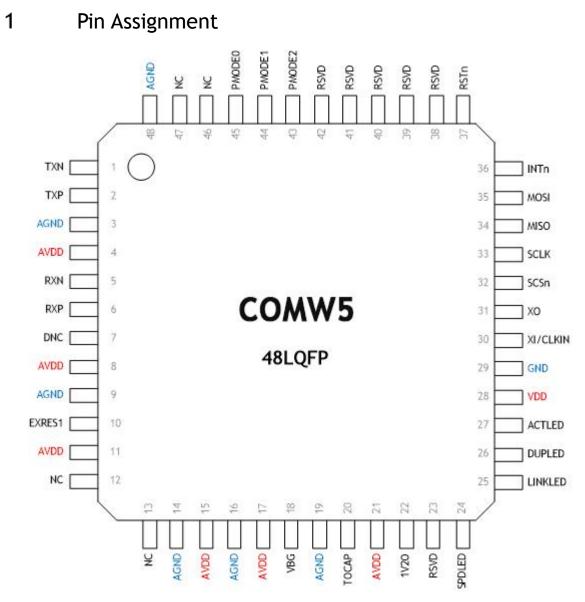

Figure 1. COMW5 Pin Layout

# 1.1 Pin Descriptions

Table 1. Pin Type Notation

| Туре | Description    |

|------|----------------|

| I    | Input          |

| 0    | Output         |

| 1/0  | Input / Output |

| А    | Analog         |

| PWR  | 3.3V power     |

| GND  | Ground         |

| Pin No | Symbol | Internal<br>Bias <sup>1</sup> | Туре | Description                                                      |  |

|--------|--------|-------------------------------|------|------------------------------------------------------------------|--|

| 1      | TXN    | -                             | AO   | TXP/TXN Signal Pair                                              |  |

| 2      | ТХР    | -                             | AO   | The differential data is transmitted to the media on the         |  |

|        |        |                               |      | TXP/TXN signal pair.                                             |  |

| 3      | AGND   | -                             | GND  | Analog ground                                                    |  |

| 4      | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 5      | RXN    | -                             | Al   | RXP/RXN Signal Pair                                              |  |

| 6      | RXP    | -                             | AI   | The differential data from the media is received on the          |  |

|        |        |                               |      | RXP/RXN signal pair.                                             |  |

| 7      | DNC    | -                             | AI/O | Do Not Connect Pin                                               |  |

| 8      | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 9      | AGND   | -                             | GND  | Analog ground                                                    |  |

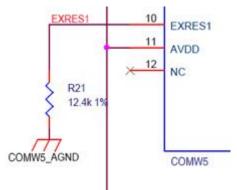

| 10     | EXRES1 | -                             | AI/O | External Reference Resistor                                      |  |

|        |        |                               |      | It should be connected to an external resistor (12.4K $\Omega$ , |  |

|        |        |                               |      | 1%) needed for biasing of internal analog circuits.              |  |

|        |        |                               |      | Refer to the 'External reference resistor' (Figure.2) for        |  |

|        |        |                               |      | details.                                                         |  |

| 11     | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 12     | -      |                               | -    | NC                                                               |  |

| 13     | -      |                               | -    | NC                                                               |  |

| 14     | AGND   | -                             | GND  | Analog ground                                                    |  |

| 15     | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 16     | AGND   | -                             | GND  | Analog ground                                                    |  |

| 17     | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 18     | VBG    | -                             | AO   | Band Gap Output Voltage                                          |  |

|        |        |                               |      | This pin will be measured as 1.2V at 25 $^\circ\!\!\mathbb{C}$ . |  |

|        |        |                               |      | It must be left floating.                                        |  |

| 19     | AGND   | -                             | GND  | Analog ground                                                    |  |

| 20     | TOCAP  | -                             | AO   | External Reference Capacitor                                     |  |

|        |        |                               |      | This pin must be connected to a 4.7uF capacitor.                 |  |

|        |        |                               |      | The trace length to capacitor should be short to                 |  |

|        |        |                               |      | stabilize the internal signals.                                  |  |

| 21     | AVDD   | -                             | PWR  | Analog 3.3V power                                                |  |

| 22     | 1V2O   | -                             | AO   | 1.2V Regulator output voltage                                    |  |

Table 2. COMW5 Pin Description

<sup>1</sup> Internal Bias after hardware reset

|    |          |           |     | This pin must be connected to a 10nF capacitor.           |  |

|----|----------|-----------|-----|-----------------------------------------------------------|--|

|    |          |           |     | This is the output voltage of the internal regulator.     |  |

| 23 | RSVD     | Pull-down | I   | It must be tied to GND.                                   |  |

| 24 | SPDLED   | -         | 0   | Speed LED                                                 |  |

|    |          |           |     | This shows the Speed status of the connected link.        |  |

|    |          |           |     | Low: 100Mbps                                              |  |

|    |          |           |     | High: 10Mbps                                              |  |

| 25 | LINKLED  | -         | 0   | Link LED                                                  |  |

|    |          |           |     | This shows the Link status.                               |  |

|    |          |           |     | Low: Link is established                                  |  |

|    |          |           |     | High: Link is not established                             |  |

| 26 | DUPLED   | -         | 0   | Duplex LED                                                |  |

|    |          |           |     | This shows the Duplex status for the connected link.      |  |

|    |          |           |     | Low: Full-duplex mode                                     |  |

|    |          |           |     | High: Half-duplex mode                                    |  |

| 27 | ACTLED   | -         | 0   | Active LED                                                |  |

|    |          |           |     | This shows that there is Carrier sense (CRS) from the     |  |

|    |          |           |     | active Physical Medium Sub-layer (PMD) during TX or RX    |  |

|    |          |           |     | activity.                                                 |  |

|    |          |           |     | Low: Carrier sense from the active PMD                    |  |

|    |          |           |     | High: No carrier sense                                    |  |

| 28 | VDD      | -         | PWR | Digital 3.3V Power                                        |  |

| 29 | GND      | -         | GND | Digital Ground                                            |  |

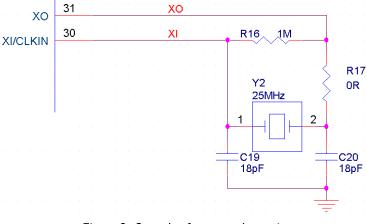

| 30 | XI/CLKIN | -         | AI  | Crystal input / External Clock input                      |  |

|    |          |           |     | External 25MHz Crystal Input.                             |  |

|    |          |           |     | This pin can also be connected to single-ended TTL        |  |

|    |          |           |     | oscillator (CLKIN). 3.3V clock should be applied for the  |  |

|    |          |           |     | External Clock input. If this method is implemented, XO   |  |

|    |          |           |     | should be left unconnected.                               |  |

|    |          |           |     | Refer to the 'Crystal reference schematic' (Figure.3) for |  |

|    |          |           |     | details.                                                  |  |

| 31 | ХО       | -         | AO  | Crystal output                                            |  |

|    |          |           |     | External 25MHz Crystal Output                             |  |

|    |          |           |     | Note: Float this pin if using an external clock being     |  |

|    |          |           |     | driven through XI/CLKIN                                   |  |

| 32 | SCSn     | Pull-up   | Ι   | Chip Select for SPI bus                                   |  |

|    |          |           |     | This pin can be asserted low to select COMW5 in SPI       |  |

|    |          |           |     |                                                           |  |

| 47 | _      | -         | - | NC                                                     |          |        |                                                |  |

|----|--------|-----------|---|--------------------------------------------------------|----------|--------|------------------------------------------------|--|

| 46 | -      | -         | - | NC                                                     |          |        |                                                |  |

|    |        |           |   |                                                        |          | 1      | את כמקמטוכי, אמנט ווכצטנומנוטוו לוומטוכע       |  |

|    |        |           |   |                                                        | 1        | 0      | Not used All capable, Auto-negotiation enabled |  |

|    |        |           |   | 1                                                      | 0        | 1      | Not used                                       |  |

|    |        |           |   | 1                                                      | 0        | 0      | 100BT Half-duplex, Auto-negotiation enabled    |  |

|    |        |           |   | 0                                                      | 1        | 1      | 100BT Full-duplex, Auto-negotiation disabled   |  |

|    |        |           |   | 0                                                      | 1        | 0      | 100BT Half-duplex, Auto-negotiation disabled   |  |

|    |        |           |   | 0                                                      | 0        | 1      | 10BT Full-duplex, Auto-negotiation disabled    |  |

|    |        |           |   | 0                                                      | 0        | 0      | 10BT Half-duplex, Auto-negotiation disabled    |  |

|    |        |           |   | 2                                                      | 1        | 0      | Description                                    |  |

|    |        |           |   | PM                                                     | ODE [2   | 2:0]   | Description                                    |  |

| 45 | PMODE0 | Pull-up   | I | _                                                      |          |        | details.                                       |  |

| 44 | PMODE1 | Pull-up   | I | _                                                      | •        |        | ermine the network mode. Refer to the          |  |

| 43 | PMODE2 | Pull-up   |   |                                                        | pera     | tion   | mode select pins                               |  |

| 42 | RSVD   | Pull-down | - | NC                                                     |          |        |                                                |  |

| 41 | RSVD   | Pull-down | - | NC                                                     |          |        |                                                |  |

| 40 | RSVD   | Pull-down |   | NC                                                     |          |        |                                                |  |

| 39 | RSVD   | Pull-down |   | NC                                                     |          |        |                                                |  |

| 38 | RSVD   | Pull-down | 1 | NC                                                     |          |        |                                                |  |

|    |        |           |   | reset.                                                 | SNOL     | ila De | e neid low at least 500 us for COMW5           |  |

|    |        |           |   | (Active                                                |          |        | e held low at least 500 us for COMW5           |  |

| 37 | RSTn   | Pull-up   | I | Reset                                                  | <b>.</b> | .)     |                                                |  |

|    |        |           |   | High:                                                  | No in    | terru  | ıpt                                            |  |

|    |        |           |   |                                                        |          | •      | asserted from COMW5                            |  |

|    |        |           |   | (Active                                                |          |        |                                                |  |

| 36 | INTn   | -         | 0 | Interr                                                 | -        | -      | ut                                             |  |

| 35 | MOSI   | -         | Ι | SPI ma                                                 | aster    | out    | out slave(COMW5) input                         |  |

|    |        |           |   | (logica                                                | ally d   | iscor  | nnected).                                      |  |

|    |        |           |   | When                                                   | SCSn     | is H   | igh, this pin becomes High Impedance           |  |

|    |        |           |   | When                                                   | SCSn     | is Lo  | ow, this pin outputs SPI data.                 |  |

| 34 | MISO   | -         | 0 | -                                                      |          |        | ut slave(COMW5) output                         |  |

| 55 | JEEK   |           |   | This pin is used to receive SPI Clock from SPI master. |          |        |                                                |  |

| 33 | SCLK   | _         |   | SPI clock input                                        |          |        |                                                |  |

|    |        |           |   | Low: selected<br>High: deselected                      |          |        |                                                |  |

| 48 | AGND | - | GND | Analog ground |

|----|------|---|-----|---------------|

|----|------|---|-----|---------------|

The 12.4K $\Omega$ (1%) Resistor should be connected between EXRES1 pin and analog ground (AGND) as below.

Figure 2. External reference resistor

The crystal reference schematic is shown as below.

# 2 HOST Interface

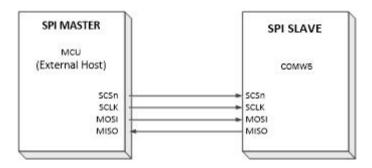

COMW5 provides SPI (Serial Peripheral Interface) Bus Interface with 4 signals (SCSn, SCLK, MOSI, MISO) for external HOST interface, and operates as a SPI Slave.

The COMW5 SPI can be connected to MCU as shown in Figure 4 and Figure 5 according to its operation mode (Variable Length Data / Fixed Length Data Mode) which will be explained in Chapter 2.3 and Chapter 2.4.

In Figure 4, SPI Bus can be shared with other SPI Devices. Since the SPI Bus is dedicated to COMW5, SPI Bus cannot be shared with other SPI Devices. It is shown in Figure 5.

At the Variable Length Data mode (as shown in Figure 4), it is possible to share the SPI Bus with other SPI devices. However, at the Fixed Length Data mode (as shown in Figure 5), the SPI Bus is dedicated to COMW5 and can't be shared with other devices.

Figure 4. Variable Length Data Mode (SCSn controlled by the host)

Figure 5. Fixed Length Data Mode (SCSn is always connected by Ground)

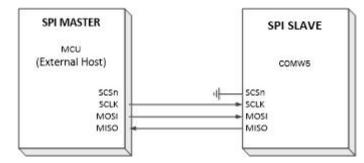

The SPI protocol defines four modes for its operation (Mode 0, 1, 2, 3).Each mode differs according to the SCLK polarity and phase. The only difference between SPI Mode 0 and SPI Mode 3 is the polarity of the SCLK signal at the inactive state.

With SPI Mode 0 and 3, data is always latched in on the rising edge of SCLK and always output on the falling edge of SCLK.

The COMW5 supports SPI Mode 0 and Mode 3. Both MOSI and MISO signals use transfer sequence from Most Significant Bit (MSB) to Least Significant Bit (LSB) when MOSI signal transmits and MISO signal receives. MOSI & MISO signals always transmit or receive in sequence from the Most Significant Bit (MSB) to Least Significant Bit (LSB).

Figure 6. SPI Mode 0 & 3

# 2.1 SPI Operation Mode

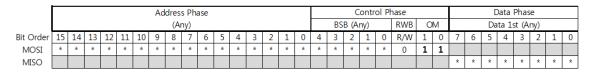

COMW5 is controlled by SPI Frame (Refer to the Chapter 2.2 SPI Frame) which communicates with the External Host. COMW5 SPI Frame consists 3 phases, Address Phase, Control Phase and Data Phase.

Address Phase specifies 16 bits Offset Address for COMW5 Register or TX/RX Memory. Control Phase specifies the block to which Offset (set by Address Phase) belongs, and specifies Read/Write Access Mode and SPI Operation Mode (Variable Length Data / Fixed Length Data Mode).

And Data Phase specifies random length (N-bytes,  $1 \leq N$ ) Data or 1 byte, 2 bytes and 4 bytes Data.

If SPI Operation Mode is set as Variable Length Data Mode (VDM), SPI Bus Signal SCSn must be controlled by the External Host with SPI Frame step.

At the Variable Length Data Mode, SCSn Control Start (Assert (High-to-Low)) informs COMW5 of SPI Frame Start (Address Phase), and SCSn Control End (De-assert (Low-to-High) informs COMW5 of SPI Frame End (Data Phase End of random N byte).

### 2.2 SPI Frame

COMW5 SPI Frame consists of 16bits Offset Address in Address Phase, 8bits Control Phase and N bytes Data Phase as shown in Figure 7.

The 8bits Control Phase is reconfigured with Block Select bits (BSB[4:0]), Read/Write Access Mode bit (RWB) and SPI Operation Mode (OM[1:0]).

Block Select bits select the block to which the Offset Address belongs.

Figure 7. SPI Frame Format

COMW5 supports Sequential Data Read/Write. It processes the data from the base (the Offset Address which is set for 2/4/N byte Sequential data processing) and the next data by increasing the Offset Address (auto increment addressing) by 1.

### 2.2.1 Address Phase

This Address Phase specifies the 16 bits Offset Address for the COMW5 Registers and TX/RX Buffer Blocks.

The 16-bit Offset Address value is transferred from MSB to LSB sequentially.

The SPI frame with 2/4/N byte data phase supports the Sequential Data Read/Write in which Offset address automatically increases by 1 every 1 byte data.

# 2.2.2 Control Phase

The Control Phase specifies the Block to which the Offset Address (set by Address Phase) belongs, the Read/Write Access Mode and the SPI Operation Mode.

| 7    | 6    | 5    | 4    | 3    | 2   | 1   | 0   |

|------|------|------|------|------|-----|-----|-----|

| BSB4 | BSB3 | BSB2 | BSB1 | BSB0 | RWB | OM1 | OM0 |

| Bit | Symbol    | Description                                                      |                                |  |  |  |  |  |

|-----|-----------|------------------------------------------------------------------|--------------------------------|--|--|--|--|--|

|     |           | Block Select Bits                                                |                                |  |  |  |  |  |

|     |           | COMW5 has Common Register, 8 Socket Register, TX/RX Buffer Block |                                |  |  |  |  |  |

|     |           | for each Socket.                                                 |                                |  |  |  |  |  |

|     |           | The next table shows th                                          | ne Block selected by BSB[4:0]. |  |  |  |  |  |

|     |           |                                                                  |                                |  |  |  |  |  |

|     |           | BSB [4:0]                                                        | Meaning                        |  |  |  |  |  |

|     |           | 00000                                                            | Selects Common Register.       |  |  |  |  |  |

|     |           | 00001                                                            | Selects Socket 0 Register      |  |  |  |  |  |

|     |           | 00010                                                            | Selects Socket 0 TX Buffer     |  |  |  |  |  |

|     |           | 00011                                                            | Selects Socket 0 RX Buffer     |  |  |  |  |  |

|     |           | 00100                                                            | Reserved                       |  |  |  |  |  |

|     |           | 00101                                                            | Selects Socket 1 Register      |  |  |  |  |  |

|     |           | 00110                                                            | Selects Socket 1 TX Buffer     |  |  |  |  |  |

| 7~3 | BSB [4:0] | 00111                                                            | Selects Socket 1 RX Buffer     |  |  |  |  |  |

|     |           | 01000                                                            | Reserved                       |  |  |  |  |  |

|     |           | 01001                                                            | Selects Socket 2 Register      |  |  |  |  |  |

|     |           | 01010                                                            | Selects Socket 2 TX Buffer     |  |  |  |  |  |

|     |           | 01011                                                            | Selects Socket 2 RX Buffer     |  |  |  |  |  |

|     |           | 01100                                                            | Reserved                       |  |  |  |  |  |

|     |           | 01101                                                            | Selects Socket 3 Register      |  |  |  |  |  |

|     |           | 01110                                                            | Selects Socket 3 TX Buffer     |  |  |  |  |  |

|     |           | 01111                                                            | Selects Socket 3 RX Buffer     |  |  |  |  |  |

|     |           | 10000                                                            | Reserved                       |  |  |  |  |  |

|     |           | 10001                                                            | Selects Socket 4 Register      |  |  |  |  |  |

|     |           | 10010                                                            | Selects Socket 4 TX Buffer     |  |  |  |  |  |

|     |           | 10011                                                            | Selects Socket 4 RX Buffer     |  |  |  |  |  |

|     |           | 10100                                                            | Reserved                       |  |  |  |  |  |

|     |           | 10101                                                            | Selects Socket 5 Register      |  |  |  |  |  |

|     |          | 10110                                                                                                                                                                                                                                 | Selects Socket 5 TX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     |          | 10111                                                                                                                                                                                                                                 | Selects Socket 5 RX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | 11000                                                                                                                                                                                                                                 | Reserved                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|     |          | 11001                                                                                                                                                                                                                                 | Selects Socket 6 Register                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |          | 11010                                                                                                                                                                                                                                 | Selects Socket 6 TX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | 11011                                                                                                                                                                                                                                 | Selects Socket 6 RX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | 11100                                                                                                                                                                                                                                 | Reserved                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|     |          | 11101                                                                                                                                                                                                                                 | Selects Socket 7 Register                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |          | 11110                                                                                                                                                                                                                                 | Selects Socket 7 TX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | 11111                                                                                                                                                                                                                                 | Selects Socket 7 RX Buffer                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | If the Reserved Bits are selected, it can cause the mal-function of the COMW5. Read/Write Access Mode Bit                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 2   | RWB      | This sets Read/Write Acc                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| -   |          | '0' : Read                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     |          | '1' : Write                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     |          | SPI Operation Mode Bits                                                                                                                                                                                                               | <u> </u>                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|     |          | This sets the SPI Operation Mode.                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     |          | SPI Operation Mode supports two modes, the Variable Length Data                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     |          | Mode and the Fixed Length Data Mode.                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 1~0 | OM [1:0] | - Variable Length Dat<br>: Data Length is con<br>External Host make<br>the start of the SPI<br>Then the externa<br>OM[1:0]='00'.<br>After N-Bytes Data<br>(Low-to-High) and i<br>COMW5.<br>In VDM Mode, the S<br>the External Host. ( | a Mode (VDM)<br>Itrolled by SCSn.<br>s SCSn Signal Assert (High-to-Low) and informs<br>Frame Address Phase to COMW5.<br>al host transfers the Control Phase with<br>a Phase transfers, SCSn Signal is De-asserted<br>informs the end of the SPI Frame Data Phase to<br>CSn must be controlled with SPI Frame unit by<br>Refer to the Figure 4) |  |  |  |  |  |

|     |          | - Fixed Length Data A                                                                                                                                                                                                                 | Node (FDM)                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| : In FD                                                 | M, the Data Length is set by OM[1:0], these are not 'O                |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| value. So, the SCSn signal should be Low state, a       |                                                                       |  |  |  |  |

| Length type (among 1 Bytes, 2 Bytes, 4 Bytes) according |                                                                       |  |  |  |  |

| OM[1:                                                   | 0] value. (Refer to the Figure 5.)                                    |  |  |  |  |

| The next                                                | table shows the SPI Operation Mode according to t                     |  |  |  |  |

| DM[1:0].                                                |                                                                       |  |  |  |  |

|                                                         |                                                                       |  |  |  |  |

|                                                         |                                                                       |  |  |  |  |

| OM[1:0]                                                 | Meaning                                                               |  |  |  |  |

| OM[1:0]<br>00                                           | Meaning<br>Variable Data Length Mode, N-Bytes Data Phase (1 $\leq$ N) |  |  |  |  |

|                                                         |                                                                       |  |  |  |  |

| 00                                                      | Variable Data Length Mode, N-Bytes Data Phase (1 $\leq$ N)            |  |  |  |  |

### 2.2.3 Data Phase

With the Control Phase set by the SPI Operation Mode Bits OM[1:0], the Data Phase is set by two types of length, one type is the N-Bytes length (VDM mode) and the other type is 1/2/4 Bytes (FDM mode).

At this time, 1 byte data is transferred through MOSI or MISO signal from MSB to LSB sequentially.

# 2.3 Variable Length Data Mode (VDM)

In VDM mode, the SPI Frame Data Phase Length is determined by SCSn Control of the External Host. That means that the Data Phase Length can have random value (Any length from 1 Byte to N Bytes) according to the SCSn Control.

The OM[1:0] of the Control Phase should be '00' value in VDM mode.

### 2.3.1 Write Access in VDM

Figure 8. Write SPI Frame in VDM mode

Figure 8 shows the SPI Frame when the external host accesses COMW5 for writing.

In VDM mode, the RWB signal is '1' (Write), OM[1:0] is '00' in SPI Frame Control Phase.

At this time the External Host assert (High-to-Low) SCSn signal before transmitting SPI Frame.

Then the Host transmits SPI Frame's all bits to COMW5 through MOSI signal. All bits are synchronized with the falling edge of the SCLK.

After finishing the SPI Frame transmit, the Host deasserts SCSn signal (Low-to-High).

When SCSn is Low and the Data Phase continues, the Sequential Data Write can be supported.

#### 1 Byte WRITE Access Example

When the Host writes Data 0xAA to 'Socket Interrupt Mask Register (SIMR) of Common Register Block by using VDM mode, the data is written with the SPI Frame below.

| Offset Address       | = 0x0018  |

|----------------------|-----------|

| BSB[4:0]             | = '00000' |

| RWB                  | = '1'     |

| OM[1:0]              | = '00'    |

| 1 <sup>st</sup> Data | = ØxAA    |

The External Host asserts (High-to-Low) SCSn before transmitting SPI Frame, then the Host transmits 1 bit with synchronizing the Toggle SCLK. The External Host deasserts (Low-to-High) the SCSn at the end of SPI Frame transmit. (Refer to the Figure 9)

| scsn      |    |    |    |    |    |    |    |      |      |     |   |   |   |   |   |   |   |   |     |      |       |      |   |   |   |   |     |       |       |     |   |   |

|-----------|----|----|----|----|----|----|----|------|------|-----|---|---|---|---|---|---|---|---|-----|------|-------|------|---|---|---|---|-----|-------|-------|-----|---|---|

|           |    |    |    |    |    |    | Ad | dres | s Ph | ase |   |   |   |   |   |   |   |   | C   | ontr | ol Pl | hase |   |   |   |   | [   | Data  | Phas  | e   |   |   |

|           |    |    |    |    |    |    |    | (0x0 | 018) |     |   |   |   |   |   |   |   |   | BSB |      |       | RWB  | 0 | M |   |   | Dat | ta 1s | t (0x | AA) |   |   |

| Bit Order | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3 | 2   | 1    | 0     | R/W  | 1 | 0 | 7 | 6 | 5   | 4     | 3     | 2   | 1 | 0 |

| MOSI      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0   | 0    | 0     | 1    | 0 | 0 | 1 | 0 | 1   | 0     | 1     | 0   | 1 | 0 |

| MISO      |    |    |    |    |    |    |    |      |      |     |   |   |   |   |   |   |   |   |     |      |       |      |   |   |   |   |     |       |       |     |   |   |

Figure 9. SIMR Register Write in VDM Mode

#### N-Bytes WRITE Access Example

When the Host writes 5 Bytes Data (0x11, 0x22, 0x33, 0x44, 0x55) to Socket 1's TX Buffer Block 0x0040 Address by using VDM mode, 5 bytes data are written with the SPI Frame below.

| Offset Address       | $= 0 \times 0040$ |  |

|----------------------|-------------------|--|

| BSB[4:0]             | = '00110'         |  |

| RWB                  | = '1'             |  |

| OM[1:0]              | = '00'            |  |

| 1 <sup>st</sup> Data | = 0x11            |  |

| 2 <sup>nd</sup> Data | = 0x22            |  |

| 3 <sup>rd</sup> Data | = 0x33            |  |

| 4 <sup>th</sup> Data | = 0x44            |  |

| 5 <sup>th</sup> Data | = 0x55            |  |

|                      |                   |  |

The N-Bytes Write Access is shown in Figure 10.

The 5 bytes of Data (0x11, 0x22, 0x33, 0x44, 0x55) are written sequentially to Socket 1's Tx Buffer Block Address  $0x0040 \sim 0x0044$ .

The External Host asserts (High-to-Low) SCSn before transmitting SPI Frame.

The External Host de-asserts (Low-to-High) the SCSn at the end of SPI Frame transmit.

Figure 10. 5 Byte Data Write at 1th Socket's TX Buffer Block 0x0040 in VDM mode

### 2.3.2 Read Access in VDM

Figure 11. Read SPI Frame in VDM mode

Figure 11 shows the SPI Frame when external host accesses COMW5 for reading In VDM mode, the RWB signal is '0' (Write), OM[1:0] is '00' in SPI Frame Control Phase.

At this time the External Host assert (High-to-Low) SCSn signal before transmitting SPI Frame.

Then the Host transmits Address and Control Phase all bits to COMW5 through MOSI signal. All bits are synchronized with the falling edge of the SCLK.

Then the Host receives all bits of Data Phase with synchronizing the rising edge of Sampling SCLK through MISO signal.

After finishing the Data Phase receive, the Host deasserts SCSn signal (Low-to-High).

When SCSn is Low and the Data Phase continues to receive, the Sequential Data Read can be supported.

#### 1 Byte READ Access Example

When the Host reads the 'Socket Status Register(S7\_SR) of the Socket 7's Register Block by using VDM mode, the data is read with the SPI Frame below. Let's S7\_SR to 'SOCK\_ESTABLISHED (0x17)'.

| Offset Address       | = | 0x0003          |

|----------------------|---|-----------------|

| BSB[4:0]             | = | ʻ11101 <i>'</i> |

| RWB                  | = | ·0,             |

| OM[1:0]              | = | · 00 ·          |

| 1 <sup>st</sup> Data | = | 0x17            |

The External Host asserts (High-to-Low) SCSn signal before transmitting SPI Frame, then the Host transmits Address and Control Phase to COMW5 through the MOSI signal. Then the Host receives Data Phase from the MISO signal.

After finishing the Data Phase receives, the Host deasserts SCSn signal (Low-to-High). (Refer to the Figure 12.)

| scsn      |    |    |    |    |    |    |    |       |      |     |   |   |   |   |   |   |   |   |     |      |       |      |   |   |   |   |    |       |        |      |   |   |  |

|-----------|----|----|----|----|----|----|----|-------|------|-----|---|---|---|---|---|---|---|---|-----|------|-------|------|---|---|---|---|----|-------|--------|------|---|---|--|

|           |    |    |    |    |    |    | Ad | dres  | s Ph | ase |   |   |   |   |   |   |   |   | C   | ontr | ol Pl | nase |   |   |   |   | [  | Data  | Phas   | se   |   |   |  |

|           |    |    |    |    |    |    |    | (0x0) | 003) |     |   |   |   |   |   |   |   |   | BSB |      |       | RWB  | 0 | М |   |   | Da | ta 1s | st (0x | (17) |   |   |  |

| Bit Order | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3 | 2   | 1    | 0     | R/W  | 1 | 0 | 7 | 6 | 5  | 4     | 3      | 2    | 1 | 0 |  |

| MOSI      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0    | 0   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1   | 0    | 1     | 0    | 0 | 0 |   |   |    |       |        |      |   |   |  |

| MISO      |    |    |    |    |    |    |    |       |      |     |   |   |   |   |   |   |   |   |     |      |       |      |   |   | 0 | 0 | 0  | 1     | 0      | 1    | 1 | 1 |  |

Figure 12. S7\_SR Read in VDM Mode

#### N-Bytes Read Access Example

When the Host reads 5 Bytes Data (0xAA, 0xBB, 0xCC, 0xDD, 0xEE) from the Socket 3's RX Buffer Block 0x0100 Address by using VDM mode, 5 bytes data are read with the SPI Frame as below.

| Offset Addre         | ss = 0x0100 |

|----------------------|-------------|

| BSB[4:0]             | = '01111'   |

| RWB                  | = '0'       |

| OM[1:0]              | = '00'      |

| 1 <sup>st</sup> Data | = ØxAA      |

| 2 <sup>nd</sup> Data | = ØxBB      |

| 3 <sup>rd</sup> Data | = ØxCC      |

| 4 <sup>th</sup> Data | = ØxDD      |

| 5 <sup>th</sup> Data | = 0xEE      |

The N-Bytes Read Access is shown in Figure 13.

The 5 bytes of Data (0xAA, 0xBB, 0xCC, 0xDD, 0xEE) are read sequentially from the Socket 3's Rx Buffer Block Address 0x0100 ~ 0x0104.

The External Host asserts (High-to-Low) SCSn before transmitting SPI Frame.

The External Host de-asserts (Low-to-High) the SCSn at the end of the SPI Frame Data Phase.

Figure 13. 5 Byte Data Read at Socket 3 RX Buffer Block 0x0100 in VDM mode

# 2.4 Fixed Length Data Mode (FDM)

The FDM mode can be used when the External Host cannot control SCSn signal. The SCSn signal should be tied to Low (Always connected to GND) and it is not possible to share the SPI Bus with other SPI Devices. (Refer to the Figure 5.)

In VDM mode, Data Phase length is controlled by SCSn control.

But in FDM mode, Data Phase length is controlled by OM[1:0] value ('01' / '10' / '11') which is the SPI Operation Mode Bits of the Control Phase.

As the SPI Frame of FDM mode is the same as SPI Frame of VDM mode (1Byte, 2 Bytes, 4 Bytes SPI Frame) except for the SCSn signal control and OM[1:0] setting, the detail about FDM mode is not described in this section.

It is not recommended to use the FDM mode unless you are in inevitable status. In addition, we use only 1/2/4 Bytes SPI Frame, as described in 'Chapter 2.4.1' & 'Chapter 2.4.2'. Using SPI Frame with other length of Data will cause malfunction of COMW5.

# 2.4.1 Write Access in FDM

#### **1 Bytes WRITE Access**

|           |    |    |    |    |    |    | Ad | dres | s Pha | ase |   |   |   |   |   |   |   |    | С    | ontr | ol Pł | nase |   |   |   |   | 0  | Data  | Phas  | e   |   |   |

|-----------|----|----|----|----|----|----|----|------|-------|-----|---|---|---|---|---|---|---|----|------|------|-------|------|---|---|---|---|----|-------|-------|-----|---|---|

|           |    |    |    |    |    |    |    | (A   | ny)   |     |   |   |   |   |   |   |   | BS | B (A | ny)  |       | RWB  | 0 | M |   |   | Da | ita 1 | st (a | ny) |   |   |

| Bit Order | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3  | 2    | 1    | 0     | R/W  | 1 | 0 | 7 | 6 | 5  | 4     | 3     | 2   | 1 | 0 |

| MOSI      | *  | *  | *  | *  | *  | *  | *  | *    | *     | *   | * | * | * | * | * | * | * | *  | *    | *    | *     | 1    | 0 | 1 | * | * | *  | *     | *     | *   | * | * |

| MISO      |    |    |    |    |    |    |    |      |       |     |   |   |   |   |   |   |   |    |      |      |       |      |   |   |   |   |    |       |       |     |   |   |

Figure 14. 1 Byte Data Write SPI Frame in FDM mode

#### 2 Bytes WRITE Access

#### Figure 15. 2 Bytes Data Write SPI Frame in FDM mode

#### 4 Bytes WRITE Access

\* \* \* \* \* \*

MOSI

MISO

\*

|           |    |    |    |    |    |    | Ad | dres | s Ph | ase |   |   |   |   |   |   |   |   | C   | ontr | ol Pł | nase |   |   |   |   | C  | Data | Phas   | e   |   |   |

|-----------|----|----|----|----|----|----|----|------|------|-----|---|---|---|---|---|---|---|---|-----|------|-------|------|---|---|---|---|----|------|--------|-----|---|---|

|           |    |    |    |    |    |    |    | (A   | ny)  |     |   |   |   |   |   |   |   |   | BSB |      |       | RWB  | 0 | М |   |   | Da | ta 1 | st (ai | ny) |   |   |

| Bit Order | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3 | 2   | 1    | 0     | R/W  | 1 | 0 | 7 | 6 | 5  | 4    | 3      | 2   | 1 | 0 |

| MOSI      | *  | *  | *  | *  | *  | *  | *  | *    | *    | *   | * | * | * | * | * | * | * | * | *   | *    | *     | 1    | 1 | 1 | * | * | *  | *    | *      | *   | * | * |

| MISO      |    |    |    |    |    |    |    |      |      |     |   |   |   |   |   |   |   |   |     |      |       |      |   |   |   |   |    |      |        |     |   |   |

|           |   |   | C  | )ata  | Phas  | e   |   |   |   |   | [  | Data   | Phas  | е   |   |   |   |   |   | Data  | a Pha | ise  |   |   |

|-----------|---|---|----|-------|-------|-----|---|---|---|---|----|--------|-------|-----|---|---|---|---|---|-------|-------|------|---|---|

|           |   |   | Da | ta 2r | nd (a | ny) |   |   |   |   | Da | ita 3i | rd (a | ny) |   |   |   |   | D | ata 4 | 4th ( | any) |   |   |

| Bit Order | 7 | 6 | 5  | 4     | 3     | 2   | 1 | 0 | 7 | 6 | 5  | 4      | 3     | 2   | 1 | 0 | 7 | 6 | 5 | 4     | 3     | 2    | 1 | 0 |

| MOSI      | * | * | *  | *     | *     | *   | * | * | * | * | *  | *      | *     | *   | * | * | * | * | * | *     | *     | *    | * | * |

| MISO      |   |   |    |       |       |     |   |   |   |   |    |        |       |     |   |   |   |   |   |       |       |      |   |   |

Figure 16. 4 Bytes Data Write SPI Frame in FDM mode

## 2.4.2 Read Access in FDM

#### 1 Byte READ Access

|           |    |    |    |    |    |    | Ad | dres | s Pha | ase |   |   |   |   |   |   |   |    | C     | ontr | ol Pł | nase |   |   |   |   | [  | Data | Phas  | e   |   |   |

|-----------|----|----|----|----|----|----|----|------|-------|-----|---|---|---|---|---|---|---|----|-------|------|-------|------|---|---|---|---|----|------|-------|-----|---|---|

|           |    |    |    |    |    |    |    | (A   | ny)   |     |   |   |   |   |   |   |   | BS | B (Ai | ny)  |       | RWB  | 0 | М |   |   | Da | ta 1 | st (A | ny) |   |   |

| Bit Order | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3  | 2     | 1    | 0     | R/W  | 1 | 0 | 7 | 6 | 5  | 4    | 3     | 2   | 1 | 0 |

| MOSI      | *  | *  | *  | *  | *  | *  | *  | *    | *     | *   | * | * | * | * | * | * | * | *  | *     | *    | *     | 0    | 0 | 1 |   |   |    |      |       |     |   |   |

| MISO      |    |    |    |    |    |    |    |      |       |     |   |   |   |   |   |   |   |    |       |      |       |      |   |   | * | * | *  | *    | *     | *   | * | * |

Figure 17. 1 Byte Data Read SPI Frame in FDM mode

#### 2 Bytes READ Access

#### Figure 18. 2 Bytes Data Read SPI Frame in FDM mode

#### 4 Bytes READ Access

|           |   |   | 0  | )ata  | Phas  | e   |   |   |   |   | [  | Data   | Phas | e   |   |   |   |   |   | Data  | Pha  | ise  |   |   |

|-----------|---|---|----|-------|-------|-----|---|---|---|---|----|--------|------|-----|---|---|---|---|---|-------|------|------|---|---|

|           |   |   | Da | ta 2r | nd (A | ny) |   |   |   |   | Da | ita 3i | d (A | ny) |   |   |   |   | D | ata 4 | th ( | Any) |   |   |

| Bit Order | 7 | 6 | 5  | 4     | 3     | 2   | 1 | 0 | 7 | 6 | 5  | 4      | 3    | 2   | 1 | 0 | 7 | 6 | 5 | 4     | 3    | 2    | 1 | 0 |

| MOSI      |   |   |    |       |       |     |   |   |   |   |    |        |      |     |   |   |   |   |   |       |      |      |   |   |

| MISO      | * | * | *  | *     | *     | *   | * | * | * | * | *  | *      | *    | *   | * | * | * | * | * | *     | *    | *    | * | * |

Figure 19. 4 Bytes Data Read SPI Frame in FDM mode

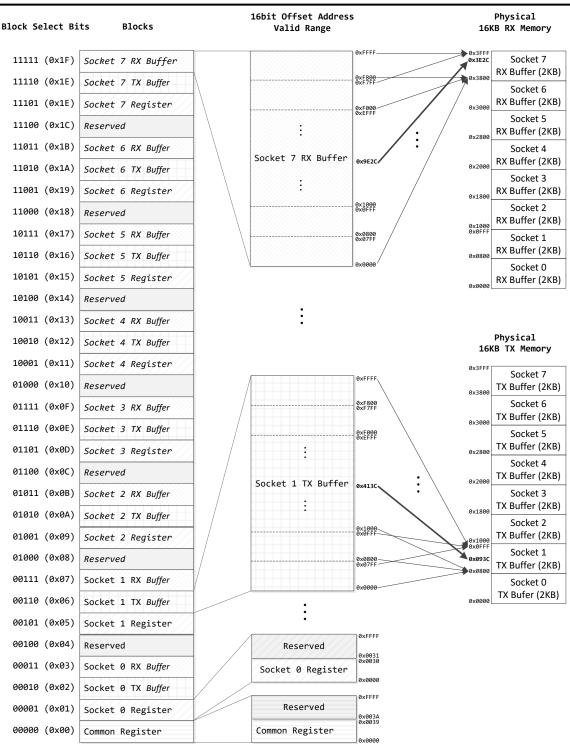

# 3 Register and Memory Organization

COMW5 has one Common Register Block, eight Socket Register Blocks, and TX/RX Buffer Blocks allocated to each Socket. Each block is selected by the BSB[4:0](Block Select Bit) of SPI Frame. Figure 20 shows the selected block by the BSB[4:0] and the available offset address range of Socket TX/RX Buffer Blocks. Each Socket's TX Buffer Block exists in one 16KB TX memory physically and is initially allocated with 2KB. Also, Each Socket's RX Buffer Block exists in one 16KB RX Memory physically and is initially allocated with 2KB.

Regardless of the allocated size of each Socket TX/RX Buffer, it can be accessible within the 16 bits offset address range (From 0x0000 to 0xFFFF).

Refer to 'Chapter 3.3' for more information about 16KB TX/RX Memory organization and access method.

Figure 20. Register & Memory Organization

# 3.1 Common Register Block

Common Register Block configures the general information of COMW5 such as IP and MAC address. This block can be selected by the BSB[4:0] value of SPI Frame. <Table 3> defines the offset address of registers in this block. Refer to 'Chapter 4.1' for more details about each register.

| Offset   | Register                | Offset   | Register                    | Offset | Register                   |

|----------|-------------------------|----------|-----------------------------|--------|----------------------------|

|          | Mode                    |          | Interrupt Low Level Timer   | 0x0021 | (PHAR3)                    |

| 0x0000   | (MR)                    | 0x0013   | (INTLEVEL0)                 | 0x0022 | (PHAR4)                    |

|          | Gateway Address         | 0x0014   | (INTLEVEL1)                 | 0x0023 | (PHAR5)                    |

| 0x0001   | (GAR0)                  |          | Interrupt                   |        | PPP Session Identification |

| 0x0002   | (GAR1)                  | 0x0015   | (IR)                        | 0x0024 | (PSID0)                    |

| 0x0003   | (GAR2)                  |          | Interrupt Mask              | 0x0025 | (PSID1)                    |

| 0x0004   | (GAR3)                  | 0x0016   | (IMR)                       |        | PPP Maximum Segment Size   |

|          | Subnet Mask Address     |          | Socket Interrupt            | 0x0026 | (PMRUO)                    |

| 0x0005   | (SUBRO)                 | 0x0017   | (SIR)                       | 0x0027 | (PMRU1)                    |

| 0x0006   | (SUBR1)                 |          | Socket Interrupt Mask       |        | Unreachable IP address     |

| 0x0007   | (SUBR2)                 | 0x0018   | (SIMR)                      | 0x0028 | (UIPRO)                    |

| 0x0008   | (SUBR3)                 |          | Retry Time                  | 0x0029 | (UIPR1)                    |

|          | Source Hardware Address | 0x0019   | (RTRO)                      | 0x002A | (UIPR2)                    |

| 0x0009   | (SHARO)                 | 0x001A   | (RTR1)                      | 0x002B | (UIPR3)                    |

| 0x000A   | (SHAR1)                 |          | Retry Count                 |        | Unreachable Port           |

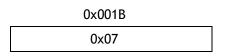

| 0x000B   | (SHAR2)                 | 0x001B   | (RCR)                       | 0x002C | (UPORTR0)                  |

| 0x000C   | (SHAR3)                 |          | PPP LCP Request Timer       | 0x002D | (UPORTR1)                  |

| 0x000D   | (SHAR4)                 | 0x001C   | (PTIMER)                    |        | PHY Configuration          |

| 0x000E   | (SHAR5)                 |          | PPP LCP Magic number        | 0x002E | (PHYCFGR)                  |

|          | Source IP Address       | 0x001D   | (PMAGIC)                    | 0x002F |                            |

| 0x000F   | (SIPRO)                 |          | PPP Destination MAC Address | ~      | Reserved                   |

| 0x0010   | (SIPR1)                 | 0x001E   | (PHAR0)                     | 0x0038 |                            |

| 0x0011   | (SIPR2)                 | 0x001F   | (PHAR1)                     |        | Chip version               |

| 0x0012   | (SIPR3)                 | 0x0020   | (PHAR2)                     | 0x0039 | (VERSIONR)                 |

| 0x003A ~ | 0xFFFF                  | Reserved |                             |        |                            |

| Table 3. Offset Address for Common Register |

|---------------------------------------------|

|---------------------------------------------|

# 3.2 Socket Register Block

COMW5 supports 8 Sockets for communication channel. Each Socket is controlled by Socket n Register Block(when  $0 \le n \le 7$ ). The n value of Socket n Register can be selected by BSB[4:0] of SPI Frame. <Table 4> defines the 16bits Offset Address of registers in Socket n Register Block.

Refer to 'Chapter 4.2' for more details about each register.

| Offset | Register                 | Offset | Register                  | Offset | Register                |  |

|--------|--------------------------|--------|---------------------------|--------|-------------------------|--|

|        | Socket n Mode            |        | Socket n Destination Port |        | Socket n TX Write       |  |

| 0x0000 | (Sn_MR)                  | 0x0010 | (Sn_DPORT0)               | 0x0024 | Pointer                 |  |

|        | Socket n Command (Sn_CR) | 0x0011 | (Sn_DPORT1)               | 0x0025 | (Sn_TX_WR0)             |  |

| 0x0001 |                          |        |                           |        | (Sn_TX_WR1)             |  |

|        |                          |        | Socket n                  |        | Socket n RX Received    |  |

|        | Socket n Interrupt       |        | Maximum Segment Size      | 0x0026 | Size                    |  |

| 0x0002 | (Sn_IR)                  | 0x0012 | (Sn_MSSR0)                | 0x0027 | (Sn_RX_RSR0)            |  |

|        |                          | 0x0013 | (Sn_MSSR1)                |        | (Sn_RX_RSR1)            |  |

|        | Socket n Status          |        |                           |        | Socket n RX Read        |  |

| 0x0003 | (Sn_SR)                  | 0x0014 | Reserved                  | 0x0028 | Pointer                 |  |

|        | Socket n Source Port     |        |                           | 0x0029 | (Sn_RX_RD0)             |  |

| 0x0004 | (Sn_PORT0)               | 0x0015 | Socket n IP TOS           |        | (Sn_RX_RD1)             |  |

| 0x0005 | (Sn_PORT1)               |        | (Sn_TOS)                  |        | Socket n RX Write       |  |

|        |                          |        | Socket n IP TTL           | 0x002A | Pointer                 |  |

|        | Socket n Destination     | 0x0016 | (Sn_TTL)                  | 0x002B | (Sn_RX_WR0)             |  |

|        | Hardware Address         |        |                           |        | (Sn_RX_WR1)             |  |

| 0x0006 | (Sn_DHAR0)               | 0x0017 |                           |        | Socket n Interrupt Mask |  |

| 0x0007 | (Sn_DHAR1)               | ~      | Reserved                  | 0x002C | (Sn_IMR)                |  |

| 0x0008 | (Sn_DHAR2)               | 0x001D |                           |        | Socket n Fragment       |  |

| 0x0009 | (Sn_DHAR3)               |        | Socket n Receive Buffer   |        | Offset in IP header     |  |

| 0x000A | (Sn_DHAR4)               | 0x001E | Size                      | 0x002D | (Sn_FRAG0)              |  |

| 0x000B | (Sn_DHAR5)               |        | (Sn_RXBUF_SIZE)           | 0x002E | (Sn_FRAG1)              |  |

|        |                          |        | Socket n                  |        |                         |  |

|        |                          | 0x001F | Transmit Buffer Size      |        | Keep alive timer        |  |

|        |                          |        | (Sn_TXBUF_SIZE)           | 0x002F | (Sn_KPALVTR)            |  |

|        | Socket n                 |        | Socket n TX Free Size     |        |                         |  |

|        | Destination IP Address   | 0x0020 | (Sn_TX_FSR0)              | 0x0030 | Reserved                |  |

| 0x000C | (Sn_DIPR0)               | 0x0021 | (Sn_TX_FSR1)              | ~      |                         |  |

| 0x000D | (Sn_DIPR1)               |        | Socket n TX Read Pointer  | 0xFFFF |                         |  |

| 0x000E | (Sn_DIPR2)               | 0x0022 | (Sn_TX_RD0)               |        |                         |  |

| 0x000F | (Sn_DIPR3)               | 0x0023 | (Sn_TX_RD1)               |        |                         |  |

Table 4. Offset Address in Socket n Register Block  $(0 \le n \le 7)$

#### 3.3 Memory

COMW5 has one 16KB TX memory for Socket n TX Buffer Blocks and one 16KB RX memory for Socket n RX buffer Blocks.

16KB TX memory is initially allocated in 2KB size for each Socket TX Buffer Block (2KB X 8 = 16KB). The initial allocated 2KB size of Socket n TX Buffer can be reallocated by using 'Socket n TX Buffer Size Register (Sn\_TXBUF\_SIZE)'.

Once all Sn\_TXBUF\_SIZE registers have been configured, Socket TX Buffer is allocated with the configured size of 16KB TX Memory and is assigned sequentially from Socket 0 to Socket 7. Its physical memory address is automatically determined in 16KB TX memory. Therefore, the total sum of Sn\_TXBUF\_SIZE should be not exceed 16 in case of error in data transmission.

The 16KB RX memory allocation method is the same as the 16KB TX memory allocation method. 16KB RX memory is initially allocated into 2KB size for each Socket RX Buffer Block (2KB X 8 = 16KB). The initial allocated 2KB size of Socket n RX Buffer can be re-allocated by using 'Socket n RX Buffer Size Register (Sn\_RXBUF\_SIZE)'.

When all Sn\_RXBUF\_SIZE registers have been configured, the Socket RX Buffer is allocated with the configured size in 16KB RX Memory and is assigned sequentially from Socket 0 to Socket 7. The physical memory address of the Socket RX Buffer is automatically determined in 16KB RX memory. Therefore, the total sum of Sn\_RXBUF\_SIZE should not exceed 16, data reception error will occur if exceeded. For 16KB TX/RX memory allocation, refer to Sn\_TXBUF\_SIZE & Sn\_RXBUF\_SIZE in 'Chapter 4.2'.

The Socket n TX Buffer Block allocated in 16KB TX memory is buffer for saving data to be transmitted by host. The 16bits Offset Address of Socket n TX Buffer Block has 64KB address space ranged from 0x0000 to 0xFFFF, and it is configured with reference to 'Socket n TX Write Pointer Register (Sn\_TX\_WR)' & 'Socket n TX Read Pointer Register(Sn\_RX\_RD)'. However, the 16bits Offset Address automatically converts into the physical address to be accessible in 16KB TX memory such as Figure 20. Refer to 'Chapter 4.2' for Sn\_TX\_WR & Sn\_TX\_RD.

The Socket n RX Buffer Block allocated in 16KB RX memory is buffer for saving the received data through the Ethernet. The 16bits Offset Address of Socket n RX Buffer Block has 64KB address space ranged from 0x0000 to 0xFFFF, and it is configured with reference to 'Socket n RX RD Pointer Register (Sn\_RX\_RD)' & 'Socket n RX Write Pointer Register (Sn\_RX\_WR)'. However, the 16bits Offset Address automatically converts into the physical address to be accessible in 16KB RX memory such as Figure 20. Refer to 'Chapter 4.2' for Sn\_RX\_RD & Sn\_RX\_WR.

# 4 Register Descriptions

# 4.1 Common Registers

#### MR (Mode Register) [R/W] [0x0000] [0x00]<sup>2</sup>

MR is used for S/W reset, ping block mode and PPPoE mode.

| 7   | 6        | 5   | 4  | 3     | 2        | 1    | 0        |

|-----|----------|-----|----|-------|----------|------|----------|

| RST | Reserved | WOL | PB | PPPoE | Reserved | FARP | Reserved |

| Bit | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | RST      | If this bit is '1', All internal registers will be initialized. It will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| /   | 1.51     | automatically cleared as '0' after S/W reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 6   | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |